N82S126/129-B,F. • S82S126

### PROGRAMMING SPECIFICATIONS (Testing of these limits may cause programming of device.) TA = +25°C

| PARAMETER                     |                            | TEST CONDITIONS                                              | LIMITS |      |      |      |

|-------------------------------|----------------------------|--------------------------------------------------------------|--------|------|------|------|

|                               |                            |                                                              | MIN    | TYP  | MAX  | UNII |

| Power Supply                  | Voltage                    |                                                              |        |      |      |      |

| VCCP1                         | To Program                 | ICCP = 350 ± 50mA                                            | 8.5    | 8.75 | 9.0  | V    |

|                               |                            | (Transient or steady state)                                  |        |      |      | - 13 |

| VCCH                          | Upper Verify Limit         |                                                              | 5.3    | 5.5  | 5.7  | ٧    |

| VCCL                          | Lower Verify Limit         |                                                              | 4.3    | 4.5  | 4.7  | ٧    |

| VS <sup>3</sup>               | Verify Threshold           | 4                                                            | 0.9    | 1.0  | 1.1  | ٧    |

| ICCP                          | Programming Supply Current | $V_{CCP} = +8.75 \pm .25V$                                   | 300    | 350  | 400  | mA   |

| Input Voltage                 |                            |                                                              |        |      |      | -    |

| VIH                           | Logical "1"                |                                                              | 2.4    |      | 5.5  | V    |

| V <sub>IL</sub>               | Logical "O"                |                                                              | 0      | 0.4  | 0.8  | V    |

| Input Current                 |                            |                                                              |        |      |      |      |

| lн                            | Logical "1"                | V <sub>IH</sub> = +5.5V                                      |        |      | 50   | μА   |

| կլ                            | Logical "O"                | V <sub>IL</sub> = +0.4V                                      |        |      | -500 | μΛ   |

| V <sub>OUT</sub> <sup>2</sup> | Output Programming Voltage | I <sub>OUT</sub> = 200 ± 20mA<br>(Transient or steady state) | 16.0   | 17.0 | 18.0 | ٧    |

| lout                          | Output Programming Current | $V_{OUT} = +17 \pm 1V$                                       | 180    | 200  | 220  | mA   |

| TR                            | Output Pulse Rise Time     | 1                                                            | 10     |      | 50   | μ6   |

| tp                            | CE Programming Pulse Width | 7                                                            | 1      |      | 2    | mi   |

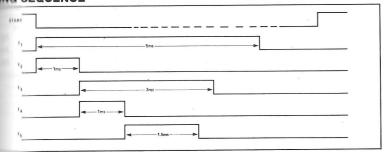

| tD                            | Pulse Sequence Delay       |                                                              | 10     |      |      | μ8   |

| TPR                           | Programming Time           | VCC = VCCP                                                   |        |      | 2.5  | 800  |

| TPS                           | Programming Pause          | VCC = OV                                                     | 5      |      |      | 800  |

| TPR + TPS                     | Programming Duty Cycle     |                                                              |        |      | 33   | %    |

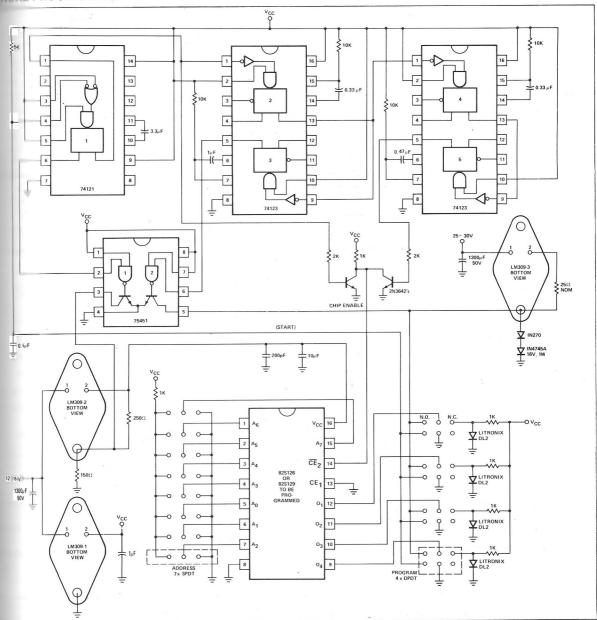

#### PROGRAMMING PROCEDURE

- Terminate all device outputs with a 10KΩ resistor to V<sub>CC</sub>.

- 2. Select the Address to be programmed, and raise VCC to  $V_{CCP} = 8.75 \pm .25V.$

- 3. After 10 $\mu$ s delay, apply VOUT =  $+17 \pm 1V$  to the output to be programmed. Program one output at the time.

- 4. After 10μs delay, pulse both CE inputs to logic "O" for 1 to 2 ms.

- After 10μs delay, remove +17V from the programmed output.

- To verify programming, after 10μs delay, lower V<sub>CC</sub> to V<sub>CCI</sub> +5.5 ± .2V, and apply a logic "0" level to both CE inputs programmed output should remain in the "1" state. Again, limit  $V_{CC}$  to  $V_{CCL}$  = +4.5  $\pm$  .2V, and verify that the programm output remains in the "1" state.

- 7. Raise VCC to VCCP = 8.75 ± .25V, and repeat steps 3 three 6 to program other bits at the same address.

- After 10μs delay, repeat steps 2 through 7 to program all θ address locations.

#### NOTES:

- 1. Bypass V<sub>CC</sub> to GND with a 0.01 pF capacitor to reduce voltage spikes.

2. Care should be taken to insure the 17 ± 1V output voltage is maintained during the entire fusing cycle. The recommended supply is a constant current source clamped at the specific age limit.

- 3. Vg is the sensing threshold of the PROM output voltage for a programmed bit. It normally constitutes the reference voltage applied to a comparator circuit to verify a successful line. tempt.

- Continuous fusing for an unlimited time is also allowed, provided that a 33% duty cycle is maintained. This may be accomplished by following each Program Verify cycle with a field (VCC = 0V) of 4ms

N82S126/129-B,F. • S82S126/129F

## **PROGRAMMER**

# MING SEQUENCE